Premium Only Content

This video is only available to Rumble Premium subscribers. Subscribe to

enjoy exclusive content and ad-free viewing.

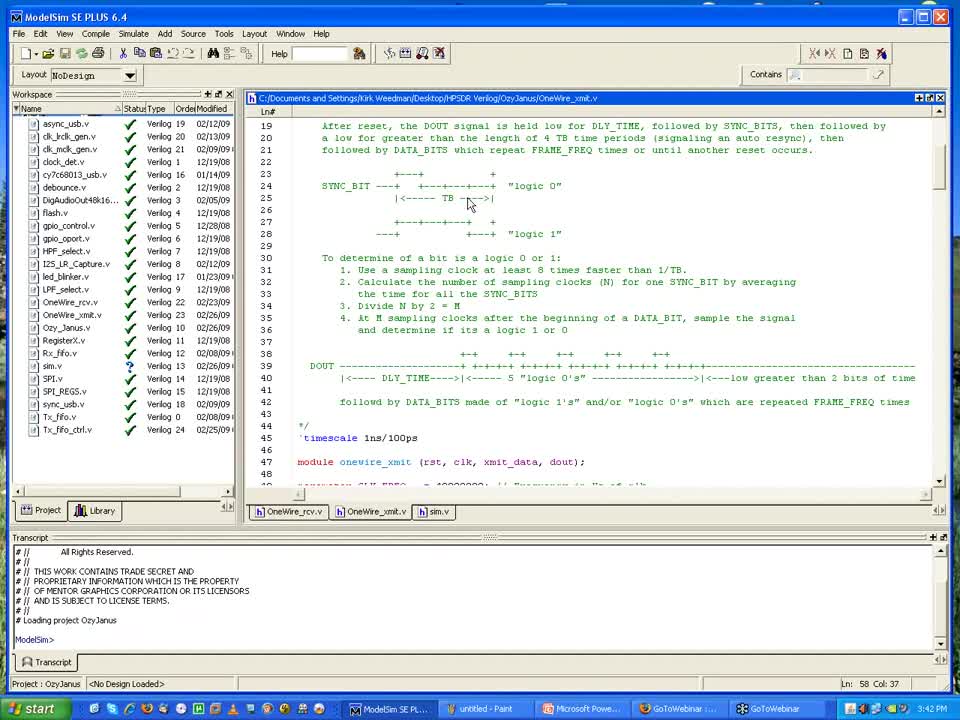

Verilog Lecture 8 of 10 - 2009

4 years ago

Verilog Basics Tutorial #8. By Kirk Weedman. see www.hdlexpress.com to download the lab files

Loading comments...

-

10:26

10:26

Atomic Bytes and EDTech

4 years agoGraphing Lecture

122 -

38:32

38:32

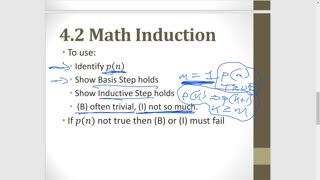

Discrete Math

4 years ago $0.09 earnedMATH 2305 Lecture 4.2

203 -

8:02

8:02

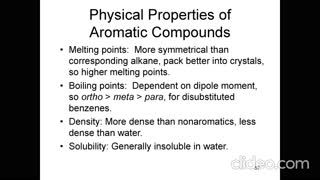

DrMardia

4 years ago $0.02 earnedLecture Number 23

99 -

11:42

11:42

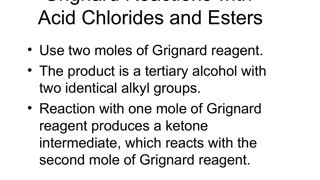

DrMardia

4 years agoLecture Number 22

45 -

8:52

8:52

DrMardia

4 years ago $0.01 earnedLecture Number 19

40 -

4:52

4:52

DrMardia

4 years agoLecture Number 17

34 -

4:52

4:52

DrMardia

4 years agoLecture Number 16

32 -

10:55

10:55

Atomic Bytes and EDTech

4 years ago $0.06 earnedAtomic History Lecture

404 -

18:10

18:10

Atomic Bytes and EDTech

4 years ago $0.04 earnedLab Equipment Lecture

95 -

4:25

4:25

DrMardia

4 years agoLecture Number 10

23