Premium Only Content

UART design in Verilog HDL with step-by-step instructions

DOWNLOAD FREE FULL COURSE

https://bit.ly/3MSlzi6

UART module comprehension and UART design using Verilog HDL programming

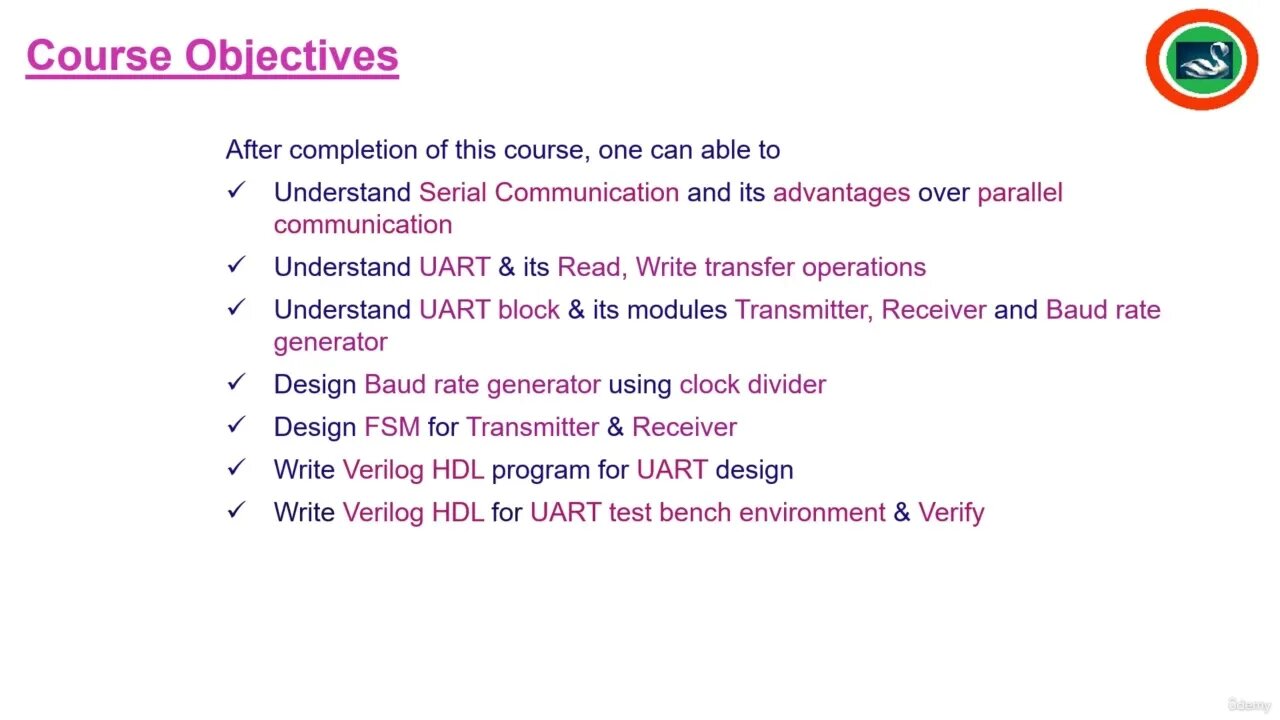

What you’ll learn

UART design in Verilog HDL with step-by-step instructions

The Advantages of Serial Communication

The Fundamentals of UART

UART design using Verilog HDL programming

Verilog HDL programming is used to simulate UART.

Requirements

Verilog HDL programming

Digital Design Fundamentals

Description

The UART Design and Simulation using Verilog HDL course provides a well-structured and clear knowledge of the UART protocol, free of any ambiguity, and it covers the principles of UART as well as the relevance of serial communication, including how it differs from parallel communication.

This course explains the capabilities of UART; how transmission and reception work in UART; and how UART data is formatted.

This course demonstrates how to use Finite State Machines to create UART internal components such as the transmitter and receiver. It explains how the baud rate generator is utilized in UART.

Students will learn how to use the test bench environment in any design or development project.

The course will also teach you how to develop Verilog HDL programs for UART modules like transmitters and receivers, as well as a baud rate generator.

Finally, it demonstrates how to write a Verilog HDL program for UART using state machine variables in detail.

This course also explains how to create a UART test bench environment. and how to choose test points in the design and move them to the test bench to verify them.

This course also goes over design verification and simulation, as well as finding errors and looking at waveforms.

Who this course is for:

Students studying electronics and communication as undergraduates

Students aiming to complete their assignments as graduates

People who work on VLSI design development

-

LIVE

LIVE

Inverted World Live

2 hours agoThe Technocratic Web of Control w/ 7SEES | Ep. 142

6,766 watching -

LIVE

LIVE

TimcastIRL

2 hours agoDemocrats COLLUDED With Epstein To HURT Trump, Emails BACKFIRE

10,761 watching -

LIVE

LIVE

Dr Disrespect

11 hours ago🔴LIVE - DR DISRESPECT - ARC RAIDERS - STELLA MONTIS QUESTS

1,609 watching -

LIVE

LIVE

SpartakusLIVE

5 hours agoSolos on WZ to Start then ARC?! || Friends: UNBANNED

242 watching -

12:58

12:58

Cash Jordan

5 hours agoMexican MOB OVERTHROWS Capital... as "Socialist President" FLOODS AMERICA with CARTELS

1801 -

23:13

23:13

Jasmin Laine

6 hours agoPBO Breaks His Silence—“This Is Soviet Stuff”… and the Panel EXPLODES

7927 -

LIVE

LIVE

Jamie Kennedy

19 hours agoCatching Up With Deep Roy: JKX Stories, Star Wars Secrets, and Total Chaos | Ep 231 HTBITY

113 watching -

LIVE

LIVE

ThisIsDeLaCruz

1 hour agoThe Secrets Behind Madonna’s Legendary Live Sound

50 watching -

1:22:15

1:22:15

Glenn Greenwald

5 hours agoTrump and JD Vance Weigh in on the MAGA Civil War Over Tucker; Zelensky's Top Associates Embroiled in $100 Million Corruption Scandal; FBI's Ongoing Concealment About Trump Shooter | SYSTEM UPDATE #548

94.3K81 -

LIVE

LIVE

megimu32

1 hour agoON THE SUBJECT: 2000s Pop Punk & Emo Nostalgia — Why It Still Hits

122 watching